DIP ବୁଝନ୍ତୁ

DIP ହେଉଛି ଏକ ପ୍ଲଗ୍-ଇନ୍। ଏହି ଉପାୟରେ ପ୍ୟାକେଜ୍ ହୋଇଥିବା ଚିପ୍ସରେ ଦୁଇଟି ଧାଡି ପିନ୍ ଥାଏ, ଯାହାକୁ DIP ଗଠନ ସହିତ ଚିପ୍ ସକେଟ୍ ସହିତ ସିଧାସଳଖ ୱେଲ୍ଡିଂ କରାଯାଇପାରିବ କିମ୍ବା ସମାନ ସଂଖ୍ୟକ ଗାତ ସହିତ ୱେଲ୍ଡିଂ ସ୍ଥିତିରେ ୱେଲ୍ଡିଂ କରାଯାଇପାରିବ। PCB ବୋର୍ଡ ପର୍ଫୋରେସନ୍ ୱେଲ୍ଡିଂ ହାସଲ କରିବା ବହୁତ ସୁବିଧାଜନକ, ଏବଂ ମଦରବୋର୍ଡ ସହିତ ଭଲ ସୁସଙ୍ଗତତା ରହିଛି, କିନ୍ତୁ ଏହାର ପ୍ୟାକେଜିଂ କ୍ଷେତ୍ର ଏବଂ ଘନତା ଅପେକ୍ଷାକୃତ ବଡ଼ ହୋଇଥିବାରୁ, ଏବଂ ପ୍ରବେଶ ଏବଂ ଅପସାରଣ ପ୍ରକ୍ରିୟାରେ ପିନ୍ କ୍ଷତିଗ୍ରସ୍ତ ହେବା ସହଜ, ଦୁର୍ବଳ ନିର୍ଭରଯୋଗ୍ୟତା।

DIP ହେଉଛି ସବୁଠାରୁ ଲୋକପ୍ରିୟ ପ୍ଲଗ୍-ଇନ୍ ପ୍ୟାକେଜ୍, ଆପ୍ଲିକେସନ୍ ପରିସରରେ ମାନକ ଲଜିକ୍ IC, ମେମୋରୀ LSI, ମାଇକ୍ରୋ କମ୍ପ୍ୟୁଟର ସର୍କିଟ୍ ଇତ୍ୟାଦି ଅନ୍ତର୍ଭୁକ୍ତ। SOJ (J-ଟାଇପ୍ ପିନ୍ ସ୍ମଲ୍ ପ୍ରୋଫାଇଲ୍ ପ୍ୟାକେଜ୍), TSOP (ପତଳା ଛୋଟ ପ୍ରୋଫାଇଲ୍ ପ୍ୟାକେଜ୍), VSOP (ଅତି ଛୋଟ ପ୍ରୋଫାଇଲ୍ ପ୍ୟାକେଜ୍), SSOP (ରିଡୁଡ୍ SOP), TSSOP (ପତଳା ହ୍ରାସ SOP) ଏବଂ SOT (ସ୍ମଲ୍ ପ୍ରୋଫାଇଲ୍ ଟ୍ରାଞ୍ଜିଷ୍ଟର), SOIC (ସ୍ମଲ୍ ପ୍ରୋଫାଇଲ୍ ଇଣ୍ଟିଗ୍ରେଟେଡ୍ ସର୍କିଟ୍), ଇତ୍ୟାଦିରୁ ପ୍ରାପ୍ତ ଛୋଟ ପ୍ରୋଫାଇଲ୍ ପ୍ୟାକେଜ୍ (SOP)।

DIP ଡିଭାଇସ୍ ଆସେମ୍ବଲି ଡିଜାଇନ୍ ତ୍ରୁଟି

PCB ପ୍ୟାକେଜ୍ ଗାତଟି ଡିଭାଇସ୍ ଅପେକ୍ଷା ବଡ଼।

PCB ପ୍ଲଗ୍-ଇନ୍ ହୋଲ୍ ଏବଂ ପ୍ୟାକେଜ୍ ପିନ୍ ହୋଲ୍ ନିର୍ଦ୍ଦିଷ୍ଟକରଣ ଅନୁସାରେ ଅଙ୍କିତ ହୋଇଥାଏ। ପ୍ଲେଟ୍ ତିଆରି ସମୟରେ ଗାତଗୁଡ଼ିକରେ ତମ୍ବା ପ୍ଲେଟିଂର ଆବଶ୍ୟକତା ହେତୁ, ସାଧାରଣ ସହନଶୀଳତା ପ୍ଲସ୍ କିମ୍ବା ମାଇନସ୍ 0.075mm ହୋଇଥାଏ। ଯଦି PCB ପ୍ୟାକେଜିଂ ହୋଲ୍ ଭୌତିକ ଡିଭାଇସର ପିନ୍ ଅପେକ୍ଷା ବହୁତ ବଡ଼ ହୋଇଥାଏ, ତେବେ ଏହା ଡିଭାଇସର ଢିଲା ହେବା, ପର୍ଯ୍ୟାପ୍ତ ଟିନ୍, ଏୟାର ୱେଲ୍ଡିଂ ଏବଂ ଅନ୍ୟାନ୍ୟ ଗୁଣବତ୍ତା ସମସ୍ୟା ସୃଷ୍ଟି କରିବ।

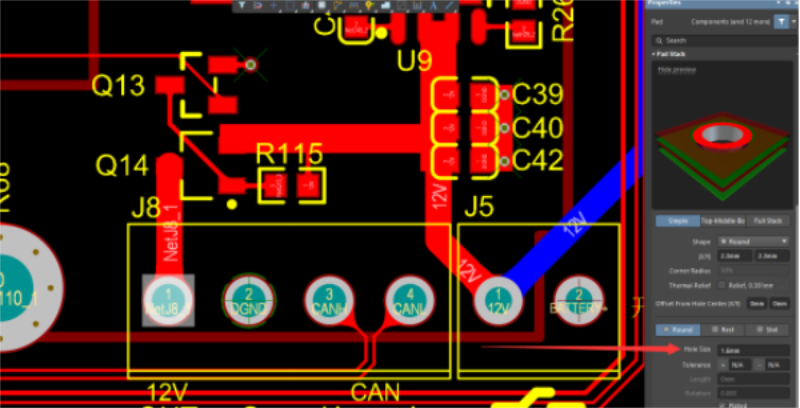

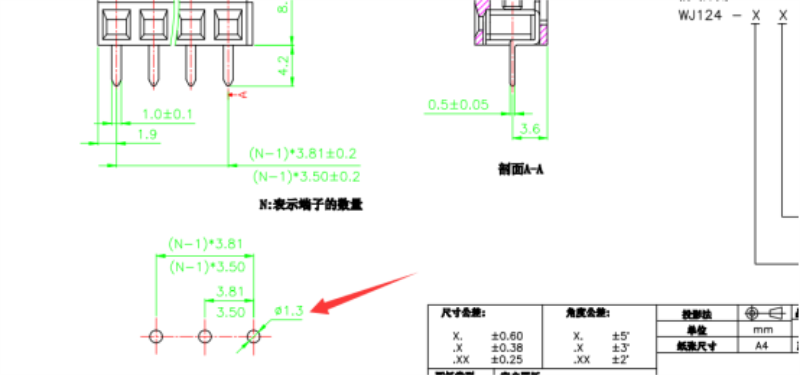

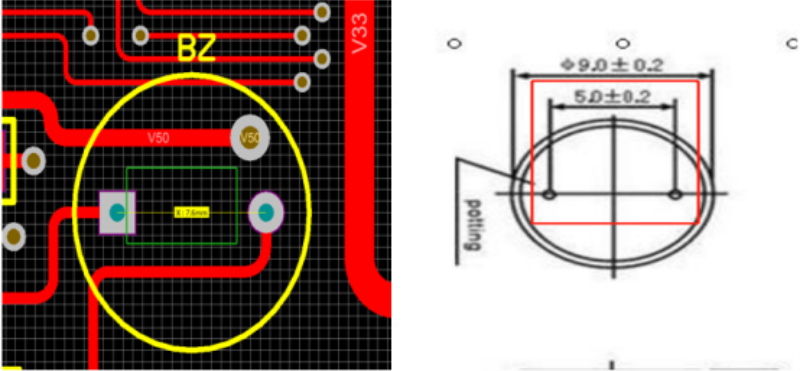

ତଳେ ଥିବା ଚିତ୍ରଟି ଦେଖନ୍ତୁ, WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) ବ୍ୟବହାର କରି ଡିଭାଇସ୍ ପିନ୍ 1.3mm, PCB ପ୍ୟାକେଜିଂ ହୋଲ୍ 1.6mm, ଆପେର୍ଚର ଅତ୍ୟଧିକ ବଡ଼ ଏବଂ ଓଭର ୱେଭ୍ ୱେଲ୍ଡିଂ ସ୍ଥାନ ସମୟ ୱେଲ୍ଡିଂ ପାଇଁ ଲିଡ୍।

ଚିତ୍ର ସହିତ ସଂଲଗ୍ନ, ଡିଜାଇନ୍ ଆବଶ୍ୟକତା ଅନୁସାରେ WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) ଉପାଦାନଗୁଡ଼ିକ କିଣନ୍ତୁ, ପିନ୍ 1.3mm ସଠିକ୍।

PCB ପ୍ୟାକେଜ୍ ଗାତ ଡିଭାଇସ୍ ଅପେକ୍ଷା ଛୋଟ।

ପ୍ଲଗ୍-ଇନ୍, କିନ୍ତୁ କୌଣସି ତମ୍ବା ଗାତ ହେବ ନାହିଁ, ଯଦି ଏହା ଏକକ ଏବଂ ଡବଲ୍ ପ୍ୟାନେଲ୍ ଅଟେ ତେବେ ଏହି ପଦ୍ଧତି ବ୍ୟବହାର କରିପାରିବେ, ଏକକ ଏବଂ ଡବଲ୍ ପ୍ୟାନେଲ୍ ବାହ୍ୟ ବୈଦ୍ୟୁତିକ ପରିବହନ, ସୋଲଡର ପରିବାହୀ ହୋଇପାରେ; ମଲ୍ଟିଲେୟାର ବୋର୍ଡର ପ୍ଲଗ୍-ଇନ୍ ଗାତ ଛୋଟ, ଏବଂ ଭିତର ସ୍ତରର ବୈଦ୍ୟୁତିକ ପରିବହନ ଥିଲେ ହିଁ PCB ବୋର୍ଡ ପୁନଃନିର୍ମାଣ କରାଯାଇପାରିବ, କାରଣ ଭିତର ସ୍ତର ପରିବାହକୁ ରିମିଂ ଦ୍ୱାରା ପ୍ରତିକାର କରାଯାଇପାରିବ ନାହିଁ।

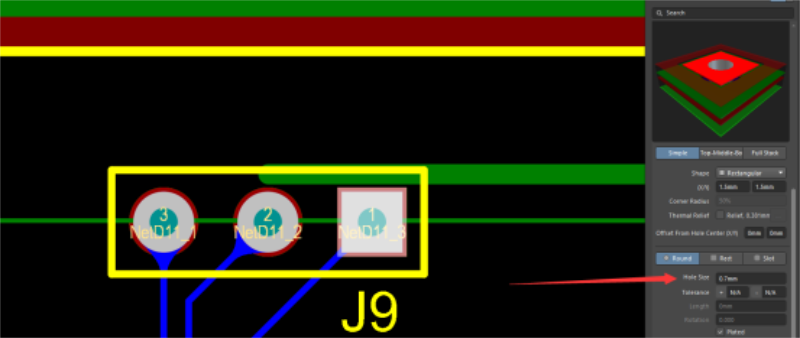

ତଳେ ଥିବା ଚିତ୍ରରେ ଦେଖାଯାଇଥିବା ପରି, A2541Hwv-3P_A2541HWV-3P (CJT) ର ଉପାଦାନଗୁଡ଼ିକ ଡିଜାଇନ୍ ଆବଶ୍ୟକତା ଅନୁସାରେ କିଣାଯାଇଛି। ପିନ୍ 1.0mm, ଏବଂ PCB ସିଲିଂ ପ୍ୟାଡ୍ ଗର୍ତ୍ତ 0.7mm, ଯାହା ଫଳରେ ଇନସାର୍ଟ ହେବାରେ ବିଫଳ ହୁଏ।

A2541Hwv-3P_A2541HWV-3P (CJT) ର ଉପାଦାନଗୁଡ଼ିକ ଡିଜାଇନ୍ ଆବଶ୍ୟକତା ଅନୁସାରେ କିଣାଯାଇଛି। ପିନ୍ 1.0mm ସଠିକ୍ ଅଛି।

ପ୍ୟାକେଜ୍ ପିନ୍ ବ୍ୟବଧାନ ଡିଭାଇସ୍ ବ୍ୟବଧାନଠାରୁ ଭିନ୍ନ ଅଟେ

DIP ଡିଭାଇସର PCB ସିଲିଂ ପ୍ୟାଡରେ କେବଳ ପିନ୍ ପରି ସମାନ ଆପେରଚର ନାହିଁ, ବରଂ ପିନ୍ ଗାତ ମଧ୍ୟରେ ସମାନ ଦୂରତା ଆବଶ୍ୟକ। ଯଦି ପିନ୍ ଗାତ ଏବଂ ଡିଭାଇସ ମଧ୍ୟରେ ବ୍ୟବଧାନ ଅସଙ୍ଗତ ଥାଏ, ତେବେ ଆଡଜଷ୍ଟେବଲ୍ ପାଦ ବ୍ୟବଧାନ ଥିବା ଅଂଶଗୁଡ଼ିକୁ ଛାଡି ଡିଭାଇସକୁ ସନ୍ନିବେଶ କରାଯାଇପାରିବ ନାହିଁ।

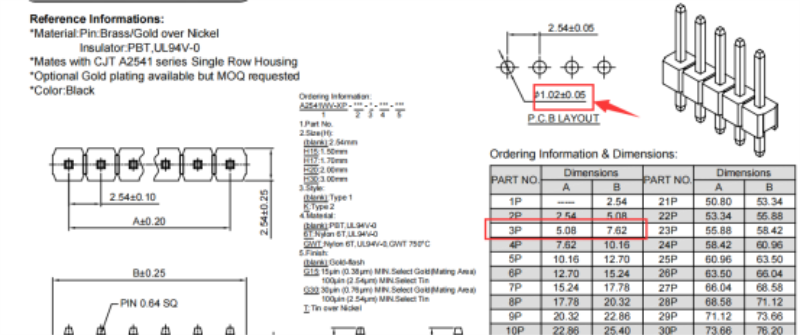

ତଳେ ଥିବା ଚିତ୍ରରେ ଦେଖାଯାଇଥିବା ପରି, PCB ପ୍ୟାକେଜିଂର ପିନ୍ ହୋଲ୍ ଦୂରତା 7.6mm, ଏବଂ କିଣାଯାଇଥିବା ଉପାଦାନଗୁଡ଼ିକର ପିନ୍ ହୋଲ୍ ଦୂରତା 5.0mm। 2.6mm ର ପାର୍ଥକ୍ୟ ଡିଭାଇସ୍ କୁ ବ୍ୟବହାରଯୋଗ୍ୟ କରିଦିଏ ନାହିଁ।

PCB ପ୍ୟାକେଜିଂ ଗାତଗୁଡ଼ିକ ବହୁତ ନିକଟତର।

PCB ଡିଜାଇନ୍, ଡ୍ରଇଂ ଏବଂ ପ୍ୟାକେଜିଂରେ, ପିନ୍ ହୋଲ୍ ମଧ୍ୟରେ ଦୂରତା ପ୍ରତି ଧ୍ୟାନ ଦେବା ଆବଶ୍ୟକ। ଯଦିଓ ଖାଲି ପ୍ଲେଟ୍ ସୃଷ୍ଟି କରାଯାଇପାରିବ, ପିନ୍ ହୋଲ୍ ମଧ୍ୟରେ ଦୂରତା କମ୍ ଥାଏ, ତରଙ୍ଗ ସୋଲଡରିଂ ଦ୍ୱାରା ଆସେମ୍ବଲି ସମୟରେ ଟିନ୍ ସର୍ଟ ସର୍କିଟ୍ ହେବା ସହଜ।

ତଳେ ଥିବା ଚିତ୍ରରେ ଦେଖାଯାଇଥିବା ପରି, ଛୋଟ ପିନ୍ ଦୂରତା ଯୋଗୁଁ ସର୍ଟ ସର୍କିଟ୍ ହୋଇପାରେ। ସୋଲଡରିଂ ଟିନ୍ରେ ସର୍ଟ ସର୍କିଟ୍ ହେବାର ଅନେକ କାରଣ ଅଛି। ଯଦି ଡିଜାଇନ୍ ଶେଷରେ ପୂର୍ବରୁ ଏକତ୍ରୀକରଣକୁ ରୋକାଯାଇପାରିବ, ତେବେ ସମସ୍ୟାର ପ୍ରକୋପ ହ୍ରାସ କରାଯାଇପାରିବ।

DIP ଡିଭାଇସ୍ ପିନ୍ ସମସ୍ୟା ମାମଲା

ସମସ୍ୟାର ବର୍ଣ୍ଣନା

ଏକ ଉତ୍ପାଦ DIP ର ୱେଭ୍ କ୍ରେଷ୍ଟ୍ ୱେଲ୍ଡିଂ ପରେ, ଜଣାପଡିଲା ଯେ ନେଟୱାର୍କ ସକେଟର ସ୍ଥିର ଫୁଟର ସୋଲ୍ଡର୍ ପ୍ଲେଟରେ ଟିନର ଗୁରୁତର ଅଭାବ ଥିଲା, ଯାହା ଏୟାର ୱେଲ୍ଡିଂ ସହିତ ଜଡିତ ଥିଲା।

ସମସ୍ୟାର ପ୍ରଭାବ

ଫଳସ୍ୱରୂପ, ନେଟୱାର୍କ ସକେଟ୍ ଏବଂ PCB ବୋର୍ଡର ସ୍ଥିରତା ଆହୁରି ଖରାପ ହୋଇଯାଏ, ଏବଂ ଉତ୍ପାଦ ବ୍ୟବହାର ସମୟରେ ସିଗନାଲ ପିନ୍ ଫୁଟର ବଳ ପ୍ରୟୋଗ କରାଯିବ, ଯାହା ଶେଷରେ ସିଗନାଲ ପିନ୍ ଫୁଟର ସଂଯୋଗକୁ ନେଇଯିବ, ଯାହା ଉତ୍ପାଦ କାର୍ଯ୍ୟଦକ୍ଷତାକୁ ପ୍ରଭାବିତ କରିବ ଏବଂ ବ୍ୟବହାରକାରୀଙ୍କ ବ୍ୟବହାରରେ ବିଫଳତାର ଆଶଙ୍କା ସୃଷ୍ଟି କରିବ।

ସମସ୍ୟା ଏକ୍ସଟେନ୍ସନ୍

ନେଟୱାର୍କ ସକେଟର ସ୍ଥିରତା ଖରାପ, ସିଗନାଲ ପିନର ସଂଯୋଗ କାର୍ଯ୍ୟଦକ୍ଷତା ଖରାପ, ଗୁଣବତ୍ତା ସମସ୍ୟା ଅଛି, ତେଣୁ ଏହା ବ୍ୟବହାରକାରୀଙ୍କ ପାଇଁ ସୁରକ୍ଷା ବିପଦ ଆଣିପାରେ, ଚୂଡ଼ାନ୍ତ କ୍ଷତି ଅକଳ୍ପନୀୟ।

DIP ଡିଭାଇସ୍ ଆସେମ୍ବଲି ବିଶ୍ଳେଷଣ ଯାଞ୍ଚ

DIP ଡିଭାଇସ୍ ପିନ୍ ସହିତ ଜଡିତ ଅନେକ ସମସ୍ୟା ଅଛି, ଏବଂ ଅନେକ ମୁଖ୍ୟ ବିନ୍ଦୁଗୁଡ଼ିକୁ ଅଣଦେଖା କରିବା ସହଜ, ଯାହାର ପରିଣାମ ସ୍ୱରୂପ ଶେଷ ସ୍କ୍ରାପ୍ ବୋର୍ଡ ହୋଇଥାଏ। ତେବେ କିପରି ଏହିପରି ସମସ୍ୟାଗୁଡ଼ିକୁ ଶୀଘ୍ର ଏବଂ ସମ୍ପୂର୍ଣ୍ଣ ଭାବରେ ଥରେ ଏବଂ ସବୁଦିନ ପାଇଁ ସମାଧାନ କରିବେ?

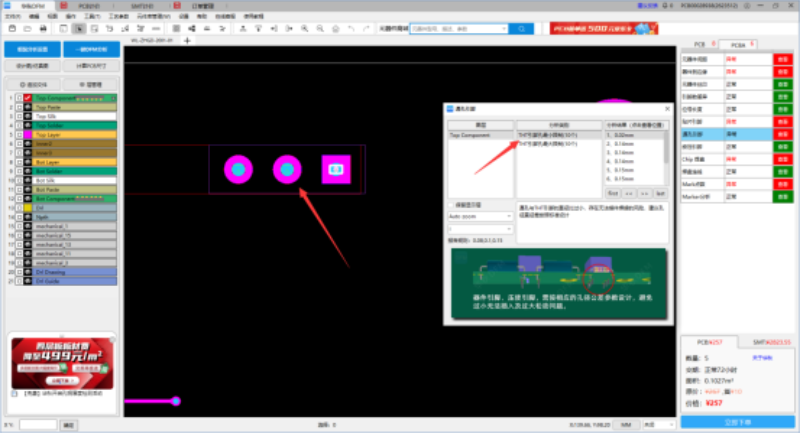

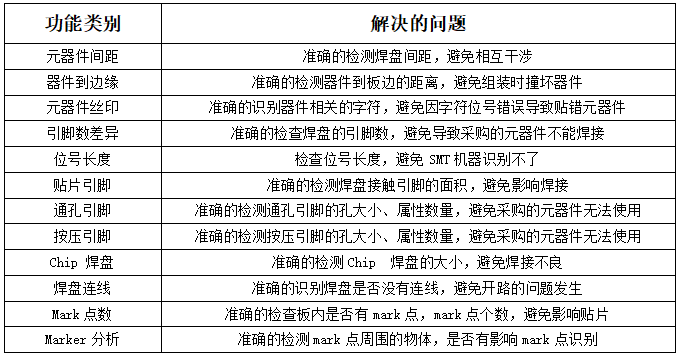

ଏଠାରେ, ଆମର CHIPSTOCK.TOP ସଫ୍ଟୱେରର ଆସେମ୍ବଲି ଏବଂ ବିଶ୍ଳେଷଣ କାର୍ଯ୍ୟକୁ DIP ଡିଭାଇସଗୁଡ଼ିକର ପିନ୍ଗୁଡ଼ିକରେ ସ୍ୱତନ୍ତ୍ର ଯାଞ୍ଚ କରିବା ପାଇଁ ବ୍ୟବହାର କରାଯାଇପାରିବ। ଯାଞ୍ଚ ଜିନିଷଗୁଡ଼ିକରେ ଗାତ ମାଧ୍ୟମରେ ପିନ୍ଗୁଡ଼ିକର ସଂଖ୍ୟା, THT ପିନ୍ଗୁଡ଼ିକର ବଡ଼ ସୀମା, THT ପିନ୍ଗୁଡ଼ିକର ଛୋଟ ସୀମା ଏବଂ THT ପିନ୍ଗୁଡ଼ିକର ଗୁଣବତ୍ତା ଅନ୍ତର୍ଭୁକ୍ତ। ପିନ୍ଗୁଡ଼ିକର ଯାଞ୍ଚ ଜିନିଷଗୁଡ଼ିକ ମୂଳତଃ DIP ଡିଭାଇସ୍ଗୁଡ଼ିକର ଡିଜାଇନ୍ରେ ସମ୍ଭାବ୍ୟ ସମସ୍ୟାଗୁଡ଼ିକୁ କଭର୍ କରେ।

PCB ଡିଜାଇନ୍ ସମାପ୍ତ ହେବା ପରେ, PCBA ଆସେମ୍ବଲି ବିଶ୍ଳେଷଣ କାର୍ଯ୍ୟକୁ ପୂର୍ବରୁ ଡିଜାଇନ୍ ତ୍ରୁଟି ଆବିଷ୍କାର କରିବା, ଉତ୍ପାଦନ ପୂର୍ବରୁ ଡିଜାଇନ୍ ଅସଙ୍ଗତି ସମାଧାନ କରିବା ଏବଂ ଆସେମ୍ବଲି ପ୍ରକ୍ରିୟାରେ ଡିଜାଇନ୍ ସମସ୍ୟାକୁ ଏଡାଇବା, ଉତ୍ପାଦନ ସମୟ ବିଳମ୍ବ କରିବା ଏବଂ ଗବେଷଣା ଏବଂ ବିକାଶ ଖର୍ଚ୍ଚ ନଷ୍ଟ କରିବା ପାଇଁ ବ୍ୟବହାର କରାଯାଇପାରିବ।

ଏହାର ଆସେମ୍ବଲି ବିଶ୍ଳେଷଣ କାର୍ଯ୍ୟରେ 10ଟି ପ୍ରମୁଖ ଜିନିଷ ଏବଂ 234ଟି ସୂକ୍ଷ୍ମ ଜିନିଷ ଯାଞ୍ଚ ନିୟମ ଅଛି, ଯାହା ଡିଭାଇସ୍ ବିଶ୍ଳେଷଣ, ପିନ୍ ବିଶ୍ଳେଷଣ, ପ୍ୟାଡ୍ ବିଶ୍ଳେଷଣ, ଇତ୍ୟାଦି ସମସ୍ତ ସମ୍ଭାବ୍ୟ ଆସେମ୍ବଲି ସମସ୍ୟାକୁ କଭର୍ କରିଥାଏ, ଯାହା ଇଞ୍ଜିନିୟରମାନେ ପୂର୍ବରୁ ଆଶା କରିପାରିବେ ନାହିଁ ଏପରି ବିଭିନ୍ନ ଉତ୍ପାଦନ ପରିସ୍ଥିତିର ସମାଧାନ କରିପାରିବ।

ପୋଷ୍ଟ ସମୟ: ଜୁଲାଇ-୦୫-୨୦୨୩